Ԫ�����ѯB���b�Y��

Ԫ������оƬ�ĶѯB���Dz��ý��I�ϵķ�ʽ��Wire Bonding�����ѯB�Ӕ����ԏ�2��8�ӣ��� STMICRO�Q���d���ȵ�40μm��оƬ���ԏ�2���ѯB��8����SRAM��Hash��DRAM����40μm��оƬ�ѯB8���� ��Ȟ�1.6 mm���ѯB�ɂ���Ȟ�0.8 mm����D1��ʾ��

�D1 Ԫ������оƬ�ĶѯB

�����ѯBԪ������Amkor PoP�����ͽY����D2��ʾ��

����·�ײ�PSvfBGA��Package Stackable very thin fine pitch BGA����

����·픲�Stacked CSP��FBGA�� Fine pitch BGA����

�D2 �ѯBԪ�������нY���D

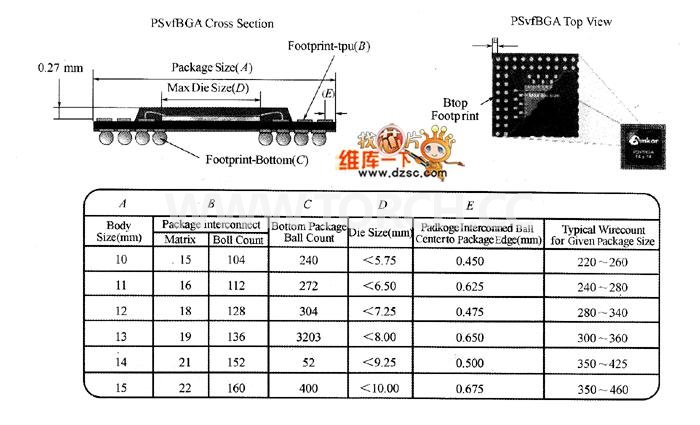

����1. �ײ� PSvfBGA��Package stackabحe very thin fine pitch BGA���Y������D3��ʾ��

����·���γߴ磺10��15 mm��

����·���g���P�g�ࣺ0.65 mm���ײ������g�ࣺ0.5 mm��0.4mm����

����·���壺FR��5��

����·������ϣ�63Sn37Pb/Pb��free��

�D3 �ײ�PSvfBGA�Y��

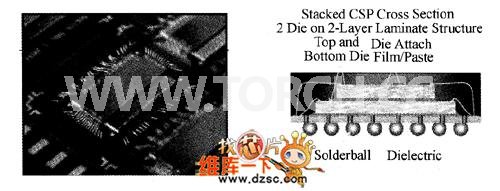

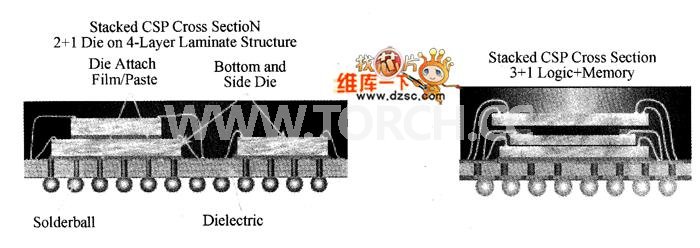

����2��픲�scsP�Y������D4�͈D5��ʾ��

����·���γߴ磺4��21 mm��

����·�ײ����g�ࣺ0.4��0.8 mm��

����·���壺 Polyimide��

����·������ϣ�63 Sn37Pb��Pb��free��

����·��0.25��0.46 mm��

�D4 픲�scsP�Y���D��1��

�D5 픲�SCSP�Y���D��2��

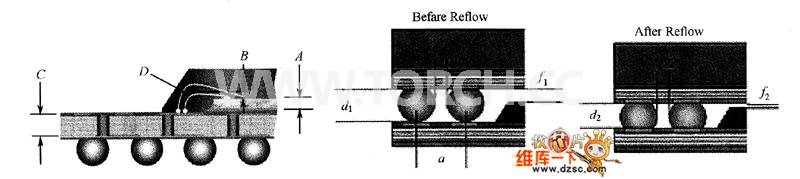

����3���ײ�Ԫ����픲�Ԫ���M�b��Ŀ��g�Pϵ����D6��ʾ��

����PoP�b������c����Ҫ����Ԫ����֮�g�Ŀ��g�Pϵ���������֮�g�]���m�����g϶����ô�͕��Б����Ĵ��ڣ����@���ڿɿ��Ժ��b�����ʁ��v��������Ӱ푡�PoP�M�b��Ŀ��g�Pϵ��D6��ʾ����������������g�Pϵ �������c��Ҫ�҂��Pע��

����·�ײ�������ģ�ܸ߶ȣ�0.27��0.35 mm����

����·픲���������ǰ����ĸ߶��c�g��e1��

����·����ǰ��픲���������͵ײ�Ԫ�������g϶fl��

����·픲�������������ĸ߶��c�g��e2��

����·������픲���������͵ײ�Ԫ�������g϶f2��

�D6 PoP�M�b����g�Pϵ

������Ӱ�����g�Pϵ�����س��˻����Ԫ�����OӋ���棬߀�л������칤ˇ��Ԫ�����b��ˇ�Լ�SMT�b�乤ˇ�������Ƕ���Ҫ�����Pע�ķ��棺

����·���P���OӋ��

����·�躸Ĥ���ڳߴ缰λ�ù��

����·����ߴ繫�

����·����߶Ȳ��

����·պȡ�����������a�������

����·�N�b�ľ��ȣ�

����·�����h���͜ضȣ�

����·Ԫ�����ͻ�����N��׃�Σ�

����·�ײ�����ģ�ܺ�ȡ�